## TEMPERATURE DEPENDENCE OF DC CURRENTS IN HBT

H.Wang, C.Algani\*, A.Konczykowska, W.Zuberek\*\*

CNET, Laboratoire de Bagneux, BP 107 - 92225 Bagneux - FRANCE.

\*: Université P. Et M.CURIE, LDIM, 4, Place Jussieu - 75005 PARIS - FRANCE.

\*\*: on leave from *Memorial University of Newfoundland*, St John's - CANADA.

### Abstract

*A DC thermal-electrical HBT model is presented in this paper. Only three parameters were needed to simulate completely an HBT with the self-heating effect, and it can be very easily implemented in any CAD softwares which use the SPICE BJT model. Parameter extractions have been carried out on several measured data and good fittings were obtained over a wide temperature range. This model is ready to be used to design high power heterojunction bipolar transistors and circuits with their thermal effects.*

Several empirical HBT thermo-electrical models have been already presented [1,2,3], and agreement with the experimental results has been obtained. Nevertheless, they are not easily usable for transistor model parameter extractions, since too many temperature parameters were needed, and they cannot be easily implemented into SPICE based CAD systems which are actually widely used.

Based on a comparative analysis of temperature effects in Si BJT's and in HBT's, a modification of the SPICE BJT model is developed for HBT in this paper. Only three parameters were needed to simulate completely an HBT with the self-heating effect, and it can be very easily implemented in any CAD softwares which use the SPICE BJT model. Parameter extractions have been carried out on several measured data and fittings were obtained over a wide temperature range.

### I. Introduction.

A good thermal-electrical CAD model of HBT is becoming very crucial for power HBT applications such as for example in mobile communication systems. Unfortunately, the HBT's thermal-electrical behaviour is very different compared to silicon bipolar transistor. For instance, the HBT's DC I-V curves show a negative slope due to its self heating effect which have never been observed in any homojunction silicon bipolar transistor. Therefore the silicon bipolar model cannot be simply adapted to HBT.

### II. Thermal-electrical model of HBT

The large signal current equations used in the present model is well-known Gummel-Poon equations for bipolar transistors used in the SPICE BJT model [4]. Among the Gummel-Poon bipolar model parameters, the current gain, the collector saturation current and recombination saturation currents dominate the transistor's DC temperature behaviour.

In our model, the ideal current gain (BF parameter in

SPICE) temperature dependence is modelled as:

$$BF = BF_0 \left( \frac{T}{T_0} \right)^p \exp \left( \frac{E_\infty}{kT} - \frac{E_\infty}{kT_0} \right)$$

where  $T$  is the junction temperature,  $k$  is the Boltzmann constant,  $BF_0$  the ideal current gain at temperature  $T_0$ , and  $E_\infty$  a positive parameter and  $p$  a real parameter characterizing the temperature behaviour of the ideal current gain.

The collector saturation current (parameter  $IS$  in SPICE) versus temperature in our model is the same as in SPICE, given by:

$$IS = IS_0 \left( \frac{T}{T_0} \right)^{XTI} \exp \left( -\frac{E_g}{kT} + \frac{E_g}{kT_0} \right)$$

where  $E_g$  is the band gap energy in the base and  $XTI$  the third temperature parameter.

It is well known that in the present state-of-the-art technology, the current gain in a HBT is limited by the non-ideal base current. In our model, the temperature dependence of the non-ideal forward base saturation current (parameter  $ISE$  in SPICE) is modelled as:

$$ISE = ISE_0 \left( \frac{IS}{IS_0} \right)^{\frac{1}{NE}} \cdot \frac{BF_0}{BF}$$

where  $NE$  is the ideal factor of the recombination current. A similar relationship is used for the reverse parameter (ISC in SPICE).

A very important feature of this model is its simplicity for implementation in any SPICE based simulation software. Only a straightforward modification, replacing the term of  $(T/T_0)^{XTB}$  of SPICE by  $\left( \frac{T}{T_0} \right)^p \exp \left( \frac{E_\infty}{kT} - \frac{E_\infty}{kT_0} \right)$  is needed. This modification has been

done in a SPICE based CAD system SPICE-PAC [5].

### III. Theoretical considerations:

The physical background of this model will be discussed in detail in the conference. Two assumptions have been used in this model:

- 1) The non-ideal base current is dominated by Shockley-Read-Hall recombination

- 2) The ideal current gain is mainly determined by the base transport factor.

These assumptions limit the validity of this model at some cases such as in high temperature (over 450K) or low base doping HBT. But for the modern HBT which combines a high base doping concentration with a matured technology minimizing the surface recombination current, this model is valid and verified by experimental results.

### IV. Experimental results

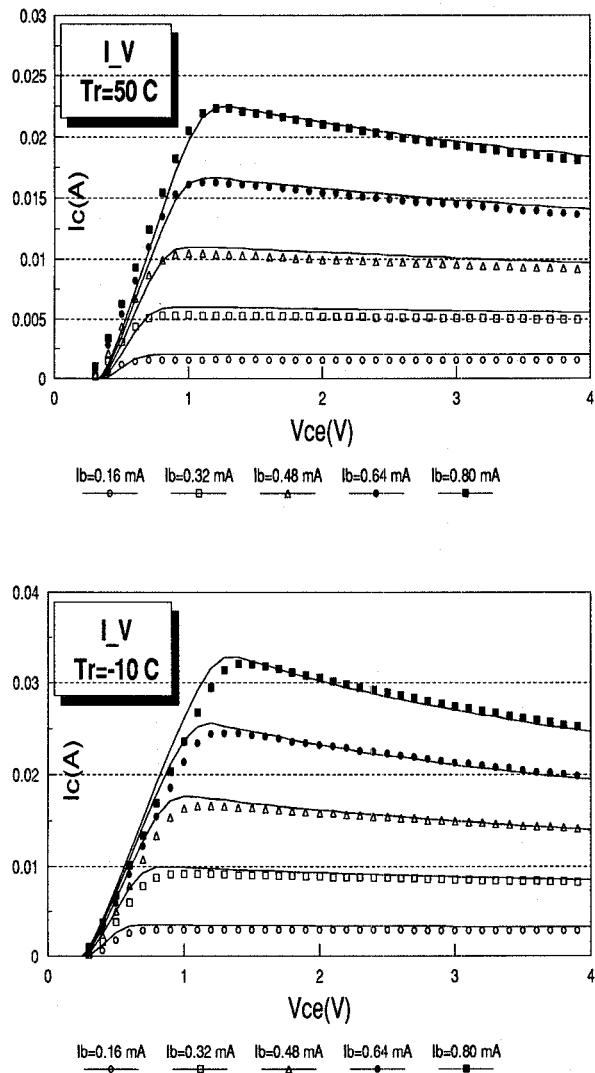

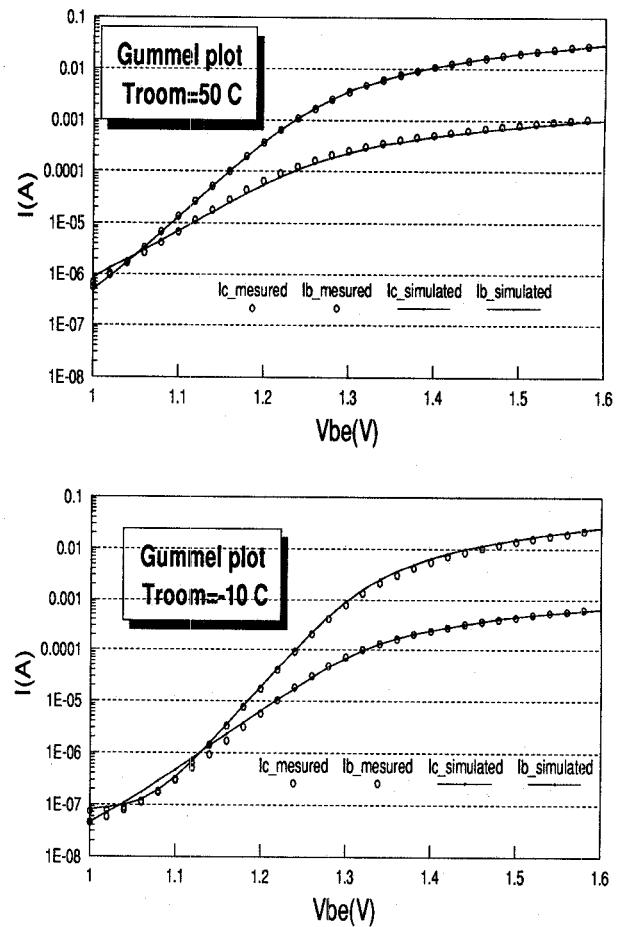

I-V characteristics and the Gummel plots of a GaAlAs/GaAs high-doped base HBT have been measured at different room temperatures, and cares have been taken to ensure that for each measurement point, the thermo-electrical steady state is reached by the transistor.

The fabrication technology used is CNET's double mesa process. The base layer thickness is about 1000 Å and the doping level is about  $3.10^{19}$  at/cm<sup>3</sup>. Combined with a graded heterojunction, it ensures that the ideal current gain is determined mainly by the base transport factor. The Early effect in this high base doping structure is negligible. This situation corresponds to a normal high speed HBT's multilayer structure. The active area of the device is 72  $\mu\text{m}^2$ .

Taking into account the self-heating effect, simulation results using our model fit perfectly each measured data at different room temperatures. Fig. 1 and Fig.2 show respectively measured and calculated I-V characteristics and Gummel Plot at  $-10^{\circ}\text{C}$  and  $50^{\circ}\text{C}$ . Fig. 3 shows the complete DC model parameters.

Figure 1. I-V characteristics measured (points) and simulated (lines) at respectively  $50^{\circ}\text{C}$  and  $-10^{\circ}\text{C}$ .

Figure 2. Gummel Plot ( $V_{BC} = 0$ ) measurement (points) and simulation (lines) at respectively  $50^{\circ}\text{C}$  and  $-10^{\circ}\text{C}$ .

|     |                                 |              |        |

|-----|---------------------------------|--------------|--------|

| Is  | $3.55 \cdot 10^{-24} \text{ A}$ | NF           | 1.027  |

| Isc | $1.10 \cdot 10^{-11} \text{ A}$ | NC           | 2.02   |

| Ise | $2.8 \cdot 10^{-17} \text{ A}$  | NE           | 1.68   |

| VAF | 600 V                           | BF           | 500    |

| p   | -1                              | XTI          | 6      |

| Rth | $690 \text{ }^{\circ}\text{W}$  | $E_{\infty}$ | 40 meV |

Figure 3. The HBT's thermo-electrical large signal model parameters.

## V. Conclusion

A SPICE-based HBT thermo-electrical large signal model which fully characterizes an HBT has been developed by changing only one term in the SPICE BJT model. Excellent fitting of model simulations with measured data has been obtained. This model is ready to be used to design high power HBTs with its self-heating effect.

## Acknowledgment.

*The authors would like to thank J.Dangla, V.Fournier, E. Zolana for their help on HBT measurements, C. Dubon-Chevallier, M. Riet and P. Berdaguer for the fabrication of HBTs, and R.Mezui, B.Sermage for helpful discussions.*

## References.

[1] P. C. GROSSMAN, A. OKI, "A large signal DC

model for GaAs/Ga<sub>1-x</sub>Al<sub>x</sub>As Heterojunction Bipolar Transistors," *IEEE Proc. Bipolar Circuits Technol. Mtg.*, Minneapolis, 18-19 Sept. 1989, pp. 258-261.

[2] H. ITO, T. ISHIBASHI, T. SUGETA, "High Current Gain AlGaAs/GaAs Heterojunction Bipolar Transistors with Heavily Doped Base," *16th Conf. Solid State Devices Mater.*, Kobe 1984, pp. 351-354.

[3] J. CHEN, G. B. GAO, H. MORKOC, "Thermal dependence of HBT high-frequency performance," *Electron. Lett.*, 11 Oct. 1990, no. 21, pp. 1770-1772.

[4] T. Quarles, et Al, "SPICE 3B1 User's Guide," University of California, Berkeley, April 1987

[5] W. M. ZUBEREK, "SPICE-PAC, a package of subroutines for interactive simulation and circuit optimization," *Proc. IEEE Int. Conf. Computer Design*, Port Chester, 1984, pp. 492-496.